# **CPC316**

**CPU Module**

# **User Manual**

Rev. 002

September 2021

Product Title:

CPC316 CPC316 User Manual Document name:

User Manual version: 002

Ref. docs:

Copyright © 2021 Fastwel Co. Ltd. All rights reserved.

## **Revision Record**

| Rev. Index | Brief Description     | Product Index | Date           |

|------------|-----------------------|---------------|----------------|

| 001        | Preliminary version   | CPC316        | April 2020     |

| 002        | Compliance assessment | CPC316        | September 2021 |

|            |                       |               |                |

#### **Contact Information**

Fastwel Co. Ltd **Fastwel Corporation US**

Address: 108 Profsoyuznaya St., 6108 Avenida Encinas,

Moscow 117437, Suite B, Carlsbad, Russian Federation CA92011, USA

Tel.: +1 (858) 488-3663 Tel.: +7 (495) 232-1681

Fax: +7 (495) 232-1654

E-mail: info@fastwel.com E-mail: info@fastwel.com

Web: http://www.fastwel.com/

# **Table of Contents**

|     | Table of Contents                                                                  |     |

|-----|------------------------------------------------------------------------------------|-----|

|     | List of Tables                                                                     | 2   |

|     | List of Figures                                                                    | 3   |

|     | Conventions                                                                        | 6   |

|     | General rules of usage                                                             |     |

|     | Manufacturer's warranties                                                          |     |

|     | Transportation, Unpacking and Storage                                              |     |

| 1   | Description and operation                                                          | 11  |

|     | 1.1 Purpose of the device                                                          | 11  |

|     | 1.2 Technical specifications                                                       | 11  |

|     | 1.3 Connection to the device                                                       |     |

|     | 1.4 Power supply                                                                   |     |

|     | 1.5 Block diagram                                                                  |     |

|     | 1.7 Versions                                                                       |     |

|     | 1.8 Delivery checklist                                                             | 19  |

|     | 1.9 Structure and functioning                                                      |     |

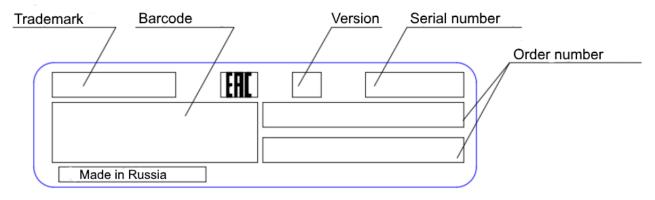

|     | 1.10 Labelling                                                                     |     |

|     | 1.11 Packaging                                                                     |     |

| 2   | Intended Use                                                                       | 40  |

|     | 2.1 Operating limitations                                                          |     |

|     | 2.2 Distribution of hardware interrupts                                            |     |

|     | 2.3 DMA channels                                                                   |     |

|     | 2.4 I/O address space                                                              |     |

|     | Memory address space                                                               |     |

|     | 2.7 WDT0 and WDT1 watchdog timers                                                  |     |

|     | 2.8 Description of internal registers                                              |     |

| _   |                                                                                    |     |

| 3   | Installation and configuration                                                     |     |

|     | 3.1 Setting the switches                                                           |     |

|     | 3.2 Configuring device parameters (BIOS SETUP)                                     | 76  |

| 4   | Software                                                                           | 77  |

|     | 4.1 Basic software                                                                 | 7   |

|     | 4.2 Establishing connection between PC and the device                              |     |

|     | 4.3 Operation of the device with AT keyboard and VGA monitor                       |     |

|     | 4.4 BIOS SOC Vortex86DX3 interface for reading serial number                       | 78  |

|     | 4.5 SOC Vortex86DX3 BIOS interface for reading/writing to FRAM4.6 Service programs |     |

|     | 4.7 BIOS Update                                                                    |     |

|     | 4.8 Switching the reference frequency for COM1, COM2, COM3, COM4                   | 80  |

|     | 4.9 Working with I2C devices.                                                      | 81  |

| 5   | Basic Input / Output System (BIOS)                                                 | 83  |

|     | 5.1 Main                                                                           | 82  |

|     | 5.2 Advanced                                                                       | 85  |

|     | 5.3 PCI / PnP                                                                      |     |

|     | 5.4 Boot                                                                           |     |

|     | 5.5 Security                                                                       |     |

|     |                                                                                    |     |

| ANN | NEX A:                                                                             | 101 |

| ANN | NEX B:                                                                             | 102 |

| ΔΝΝ | NEX C: DISCLAIMER                                                                  | 105 |

| '   | ···                                                                                |     |

# **List of Tables**

| Table 1-1:                 | Terminal board TIB972-01 (Talbe of pins)                       | 14 |

|----------------------------|----------------------------------------------------------------|----|

| Table 1-2:                 | Requirements for the external power supply parameters          | 15 |

| Table 1-3:                 | Purpose of the power supply connector pins                     | 15 |

| Table 1-4:                 | Purpose oft he pins of RS-422/485 (XP8, XP4) ports             |    |

| Table 1-5:                 | Configuration of the COM3 (X6) port                            |    |

| Table 1-6:                 | Configuration of the COM4 (X7) port                            |    |

| Table 1-7:                 | Purpose of the pins of RS-232 (XP13, XP14) ports               |    |

| Table 1-8:                 | Frequency divider values for serial ports                      |    |

| Table 1-0.                 | Purpose of pins of the USB (XP19) ports                        |    |

| Table 1-9.                 | Purpose of pins of the LAN1 (XP10) port                        |    |

|                            |                                                                |    |

| Table 1-11:                | Purpose of pins of the LAN2 (XP15) port                        |    |

| Table 1-12:                | Binding levels of UNIO ports lines (X20)                       |    |

| Table 1-13:                | Purpose of the pins of DIO (UNIO IO_A[23:0], XP16) connector   |    |

| Table 1-14:                | Purpose of pins of the DIO (UNIO IO_B[23:0], XP18) connector   |    |

| Table 1-15:                | Purpose of the VGA port pins (XP2)                             |    |

| Table 1-16:<br>Table 1-17: | Purpose of LVDS (XP3) port pins                                |    |

|                            | Purpose of Audio ports pins (XP17, XP6)                        |    |

| Table 1-18:                | Purpose of XS1 connector pins: PC/104 (ISA 8/16-bit) rows C, D |    |

| Table 1-19:<br>Table 1-20: | Purpose of XS1 connector pins: PC/104 (ISA 6/10-bit) rows C, D |    |

| Table 1-20.                | Purpose of XS2 connector pins: PCI/104 (PCU 32-bit) rows C, D  |    |

| Table 1-21.                | Purpose of device LEDs                                         |    |

| Table 1-22.                | Purpose of pins of XP9 indication connector                    |    |

| Table 1-23.                | Purpose of ADC channels ADC_AUX [7:0]                          |    |

| Table 1-24.                | Purpose of GPIO (XP1) port pins                                |    |

| Table 1-25.                | Addresses of hardware interrupts                               |    |

| Table 2-1.<br>Table 2-2:   | DMA channels of the device                                     |    |

| Table 2-2:<br>Table 2-3:   | Distribution of I/O address space                              |    |

| Table 2-3:<br>Table 2-4:   | Addresses of memory devices                                    |    |

| Table 2-4:<br>Table 2-5:   | GPIO control registers                                         |    |

| Table 2-6:                 | Purpose of GPIO ports                                          |    |

| Table 2-7:                 | WDT0 restart register                                          |    |

| Table 2-8:                 | Index register of the WDT0 port address                        |    |

| Table 2-9:                 | Data register of the WDT0 port                                 |    |

| Table 2-10:                | Register of WDT0 timer control                                 |    |

| Table 2-11:                | Register of WDT1 event selection                               |    |

| Table 2-12:                | Register CNT0 of the WDT0 timer value                          |    |

| Table 2-13:                | Register CNT1 of the WDT0 timer value                          |    |

| Table 2-14:                | Register CNT2 of WDT0 timer value                              |    |

| Table 2-15:                | WDT0 timer state register                                      |    |

| Table 2-16:                | WDT1 restart register                                          |    |

| Table 2-17:                | WDT1 timer control register                                    | 47 |

| Table 2-18:                | WDT1 event selection register                                  | 47 |

| Table 2-19:                | Register CNT0 of WDT1 timer value                              | 47 |

| Table 2-20:                | Register CNT1 of WDT1 timer value                              | 48 |

| Table 2-21:                | Register CNT2 of WDT1 timer value                              | 48 |

| Table 2-22:                | WDT1 timer state register                                      |    |

| Table 2-23:                | Table of external connections for "n00" firmware               | 60 |

| Table 2-24:                | Table of "p55" firmware registers                              |    |

| Table 2-25:                | External connections for the "p55" firmware                    | 64 |

| Table 2-26:                | External connections for the "c02» firmware                    |    |

| Table 2-27:                | Ranges of the "q04" conditioner                                |    |

| Table 2-28:                | External connections for the "q04" firmware                    |    |

| Table 2-29:                | Table of external connections for "t00" firmware               |    |

| Table 3-1:                 | Purpose of switches for device configuration                   |    |

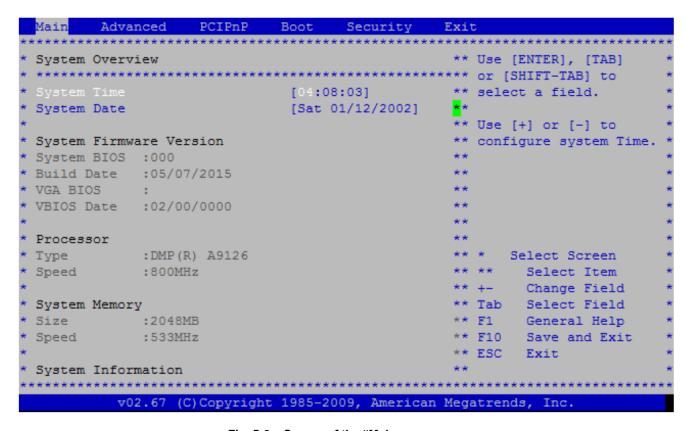

| Table 5-1:                 | Description of the "Main" menu                                 | 84 |

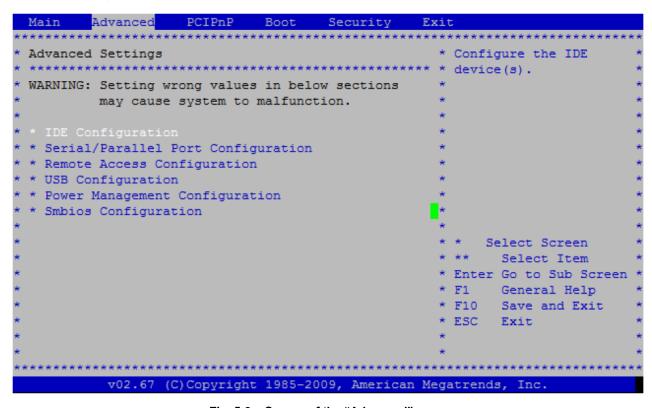

| Table 5-2:   | Description of the "Advanced" menu                                                            | 85   |

|--------------|-----------------------------------------------------------------------------------------------|------|

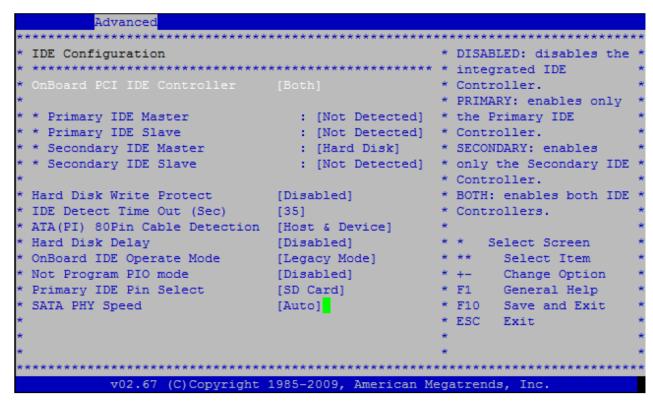

| Table 5-3:   | Description of the "IDE Configuration" menu                                                   | 86   |

| Table 5-4:   | Description of the "Primary IDE Master" menu                                                  |      |

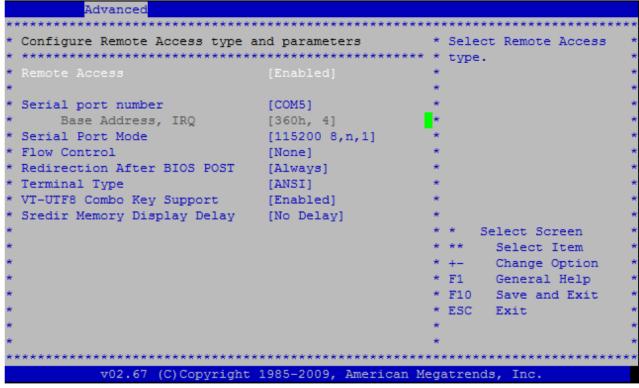

| Table 5-5:   | Description of the "Remote Access Configuration" menu                                         | 90   |

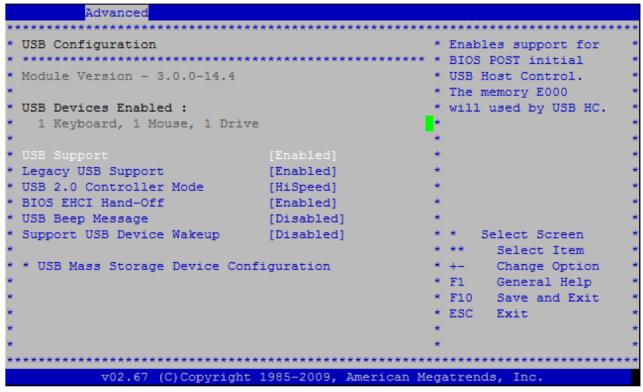

| Table 5-6:   | Description of the "USB Configuration" menu                                                   | 92   |

| Table 5-7:   | Description of the "PCI/ PnP" menu                                                            |      |

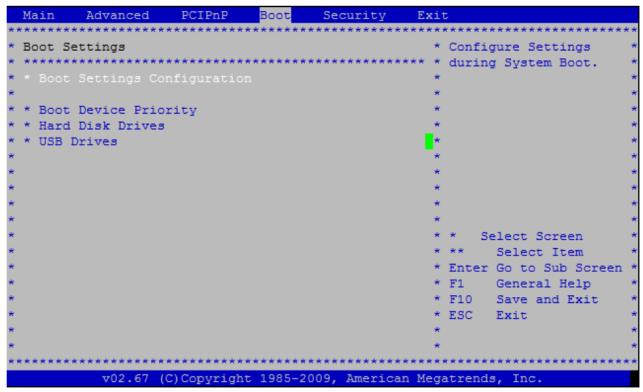

| Table 5-8:   | Description of the "Boot" menu                                                                | 95   |

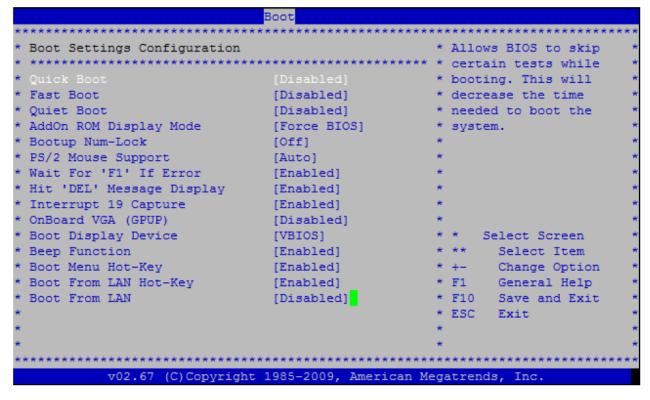

| Table 5-9:   | Description of the "Boot Settings Configuration" menu                                         | 96   |

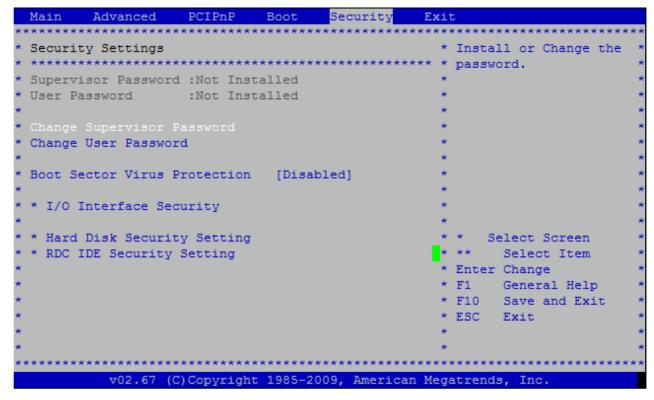

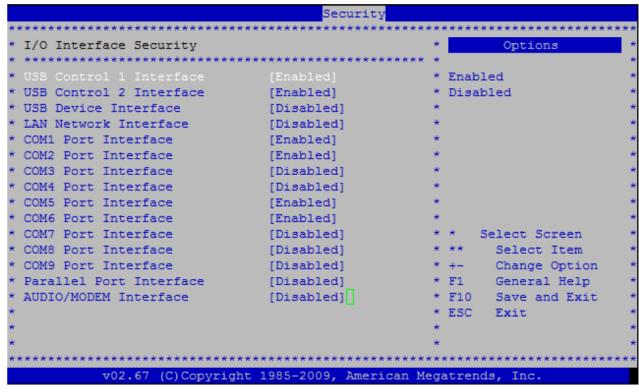

| Table 5-10:  | Description of the "Security» menu                                                            |      |

| Table 5-11:  | Description of the "SouthBridge Configuration" menu                                           | 99   |

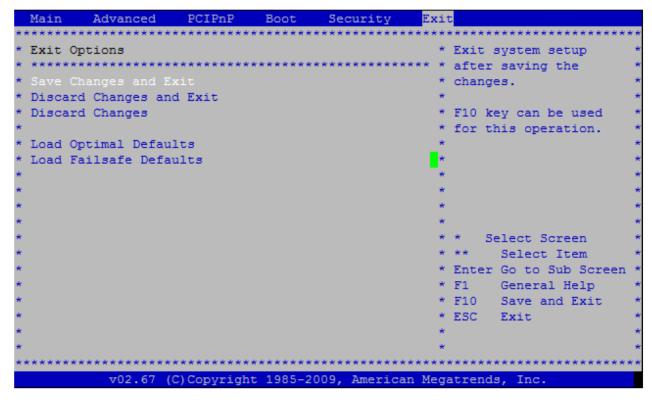

| Table 5-12:  | Description of the "Exit» menu (output)                                                       | 100  |

| List of Fig  | jures                                                                                         |      |

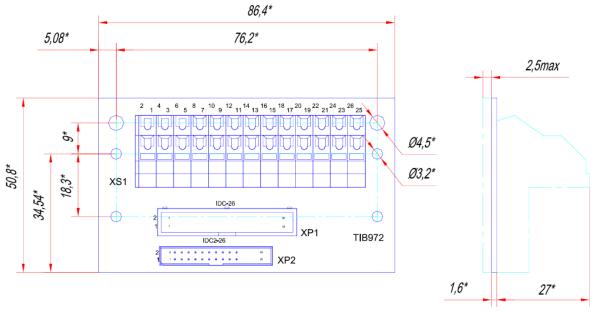

| Figure 1-1:  | Terminal board TIB972-01                                                                      | 14   |

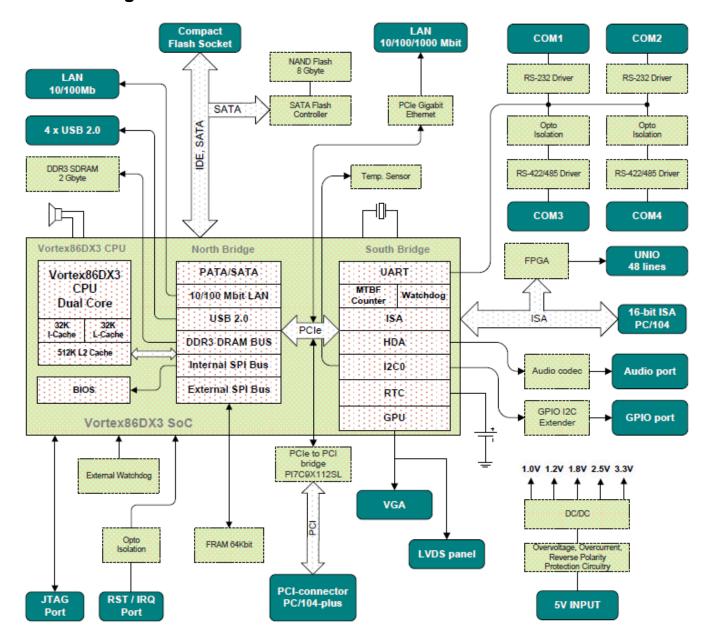

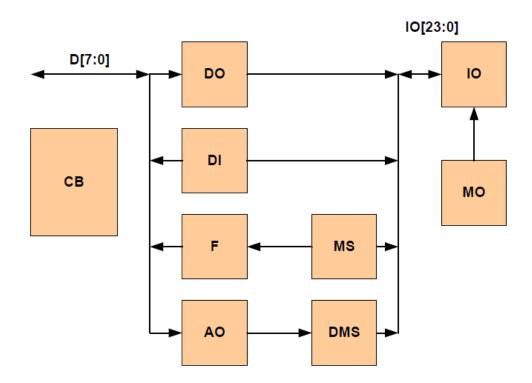

| Figure 1-2:  | Block diagram of the device                                                                   | 16   |

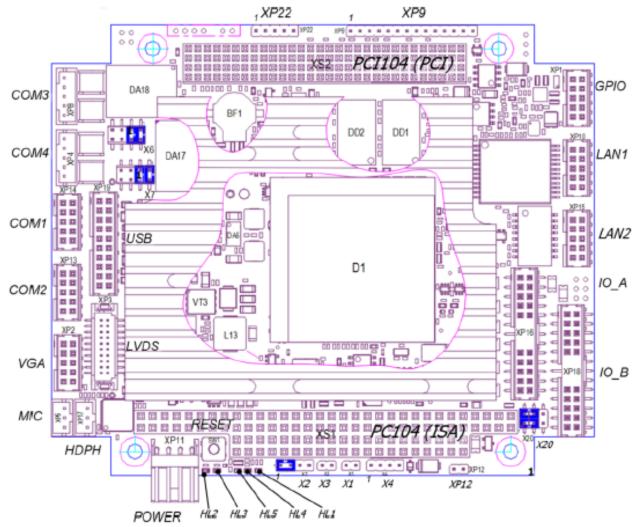

| Figure 1-3:  | Location of main elements of the device on the top side of the board                          |      |

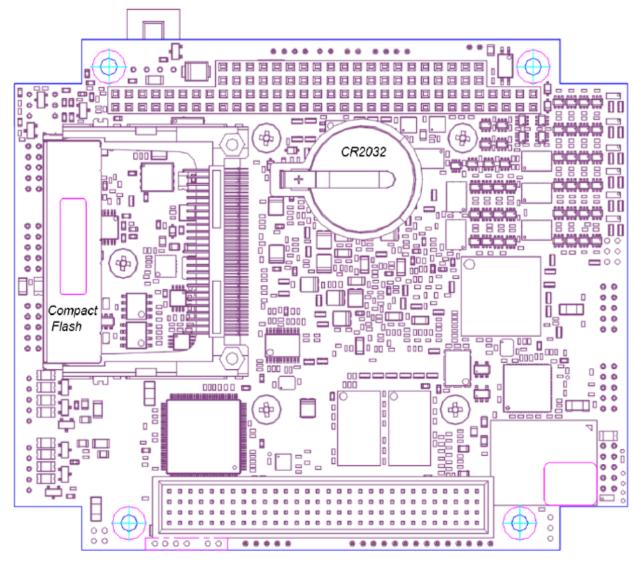

| Figure 1-4:  | Location of the main elements of the device on the bottom side of the board                   | 18   |

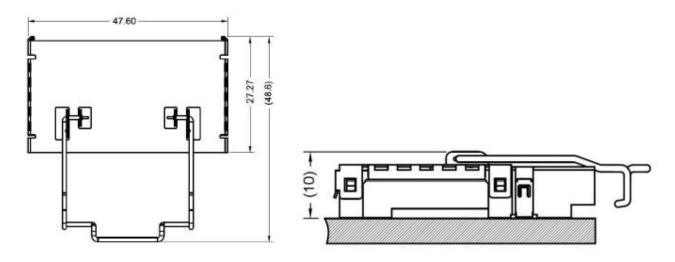

| Figure 1-5:  | Fastener for Compact Flash                                                                    | 21   |

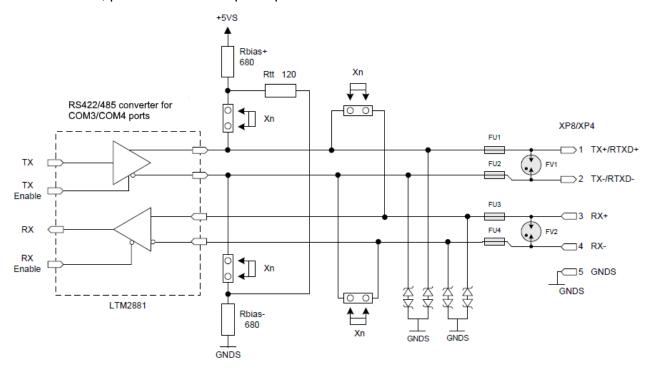

| Figure 1-6:  | Output stages of RS-422/485 ports of the device                                               | 23   |

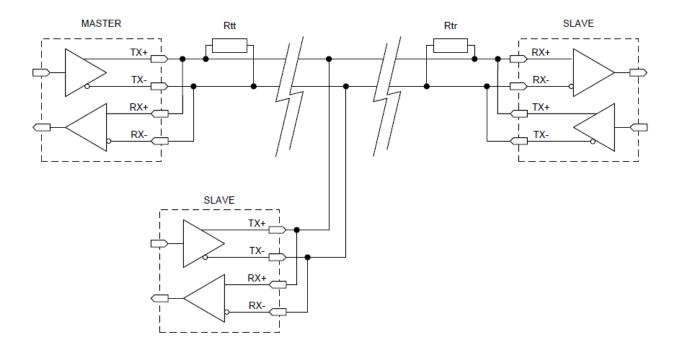

| Figure 1-7:  | Connecting modeules via RS-485 interface                                                      |      |

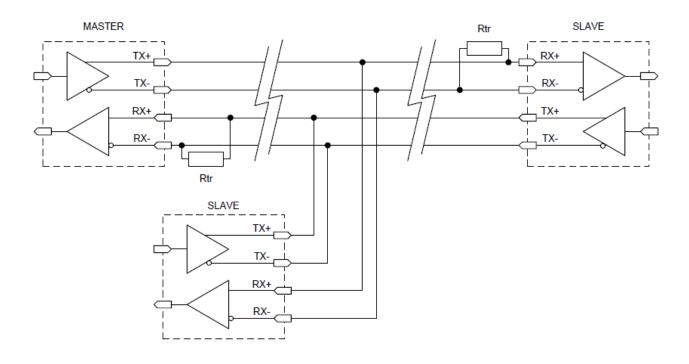

| Figure 1-8:  | Connecting modules via RS-422 interface                                                       | 24   |

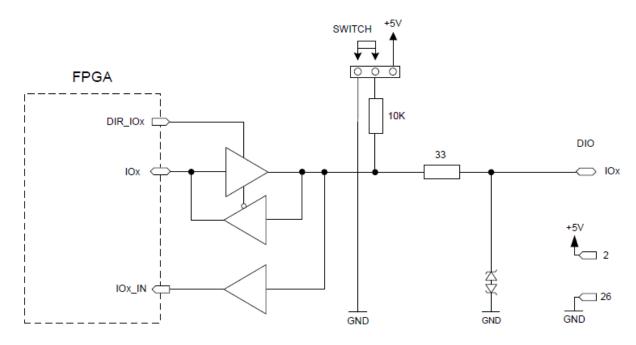

| Figure 1-9:  | Diagram of one channel of the port of digital input-output                                    | 28   |

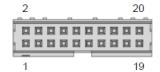

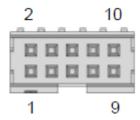

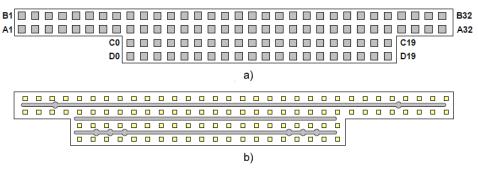

| Figure 1-10: | Numbering pins of the XS1 connector a) top view of the device, b) bottom view of the device   | with |

|              | the organizer installed into connector                                                        | 34   |

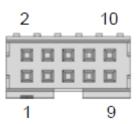

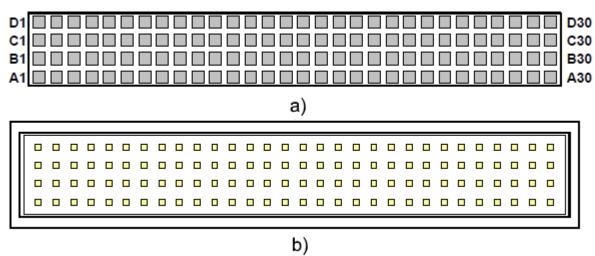

| Figure 1-11: | Numbering XS2 connector pins a) top view of the device, b) bottom view of the device with the | ne   |

| _            | organizer installed into connector                                                            | 36   |

| Figure 5-1:  | Screen during the device boot (POST)                                                          | 83   |

| Figure 5-2:  | Screen of the "Main» menu                                                                     | 84   |

| Figure 5-3:  | Screen of the "Advanced" menu                                                                 | 85   |

| Figure 5-4:  | Screen of the "IDE Configuration" menu                                                        | 86   |

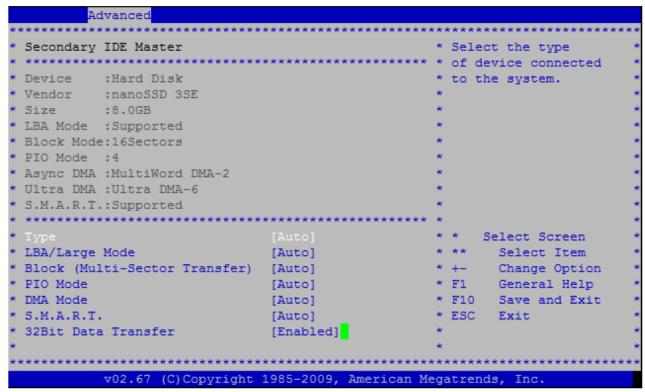

| Figure 5-5:  | Screen of the "Secondary IDE Master" menu                                                     | 88   |

| Figure 5-6:  | Screen of the "Remote Access Configuration" menu                                              | 90   |

| Figure 5-7:  | Screen of the "USB Configuration" menu                                                        |      |

| Figure 5-8:  | Screen of the "PCI/ PnP" menu                                                                 | 93   |

| Figure 5-9:  | Screen of the "Boot" menu                                                                     |      |

| Figure 5-10: | Screen of the "Boot Settings Configuration" menu                                              |      |

| Figure 5-11: | Screen of the "Security" menu                                                                 |      |

| Figure 5-12: | Screen of the "SouthBridge Configuration" menu                                                |      |

| Figure 5-13: | Screen of the "Exit" menu                                                                     | 100  |

|              |                                                                                               |      |

All information in this document is provided for reference only, with no warranty of its suitability for any specific purpose. This information has been thoroughly checked and is believed to be entirely reliable and consistent with the product that it describes. However, Fastwel accepts no responsibility for inaccuracies, omissions or their consequences, as well as liability arising from the use or application of any product or example described in this document.

Fastwel Co. Ltd. reserves the right to change, modify, and improve this document or the products described in it, at Fastwel's discretion without further notice. Software described in this document is provided on an "as is" basis without warranty. Fastwel assumes no liability for consequential or incidental damages originated by the use of this software

This document contains information, which is property of Fastwel Co. Ltd. It is not allowed to reproduce it or transmit by any means, to translate the document or to convert it to any electronic form in full or in parts without antecedent written approval of Fastwel Co. Ltd. or one of its officially authorized agents.

Fastwel logo are trademarks owned by Fastwel Co. Ltd., Moscow, Russian Federation. CompactPCI is a trademark of the PCI industrial Computers Manufacturers Group. Ethernet is a registered trademark of Kerox Corporation. IEEE is a registered trademark of the Institute of Electrical and Electronics Engineers Inc. Intel is a trademark of Intel Corporation. Pentium M and Celeron M are trademarks of Intel Corporation. Microsoft is a trademark of the Microsoft Corporation. In addition, this document may include names, company logos and trademarks, which are registered trademarks and, therefore, are property of their respective owners.

Fastwel welcomes suggestions, remarks and proposals regarding the form and the content of this Manual.

This User Manual is designed for providing you with the operating principle and general information required for commissioning, intended use and maintenance of the CPC316 CPU module IMES.467444.114 (hereinafter referred to as the "device" or the "product") manufactured by Fastwel Group.

The device is made in PC/104-plus format and is designed for use in various embedded systems that require operation in an extended temperature range (from -40 to +85 °C), compatibility of applications with x86 architecture of CPUs, as well as a combination of high performance and low level of generated thermal power and power consumption.

The document is designed for developers of distributed control and data collection systems, process control systems and embedded control systems, for system administrators and engineers of the industrial automation area.

# **Ownership rights**

This document contains information that is the property of Fastwel Group. It may not be copied or transmitted by any known means, nor may it be stored in information storage and retrieval systems without the prior written consent of Fastwel Group or one of its authorized agents. The information contained in this document, to the best of our knowledge, is free from any errors, however, Fastwel Group accepts no responsibility for any inaccuracies and their consequences, as well as liability arising from the use or application of any diagram, product or example given in this document. Fastwel Group reserves the right to change and improve both this document and the product presented inside of it at its discretion without any further notice.

# Safety requirements

This Fastwel Group's product is developed and tested for the purpose of ensuring compliance to the electric safety requirements. Its design provides long-term trouble-free operation. The service life of the product can be significantly reduced due to the improper handling during unpacking and installation. Therefore, in the interests of your safety and in order to ensure proper operation of the product, you should follow the recommendations below.

# **Conventions**

# Caution, High Voltage!

This sign and text warn of the dangers associated with electrical discharges (> 60 V) when touching the device or any part of it. Failure to follow the precautions mentioned or prescribed in the regulations may endanger your life or health, and may result in damages to the equipment. Please also read the below subparagraph dedicated to the rules for working with high voltage.

#### Attention! Static-sensitive device!

This sign and text indicate that electronic boards and their components are sensitive to static electricity, so care should be taken when handling this device and performing inspections to ensure integrity and functionality of the device.

#### Attention! Hot surface!

This sign and text warn of the danger associated with touching hot surfaces of the device.

#### Attention!

This sign is aimed at drawing your attention to aspects of this User Manual that, if not fully understood or ignored, may endanger your health or cause damages to the equipment.

#### Note

This sign is used to text fragments that should be read carefully.

# Safety requirements

This Fastwel Group product has been developed and tested to ensure compliance with electrical safety requirements. Its design provides long-term fail-safe operation. The product's life cycle may be significantly shortened due to mishandling during unpacking and installation. Therefore, for your own safety and for ensuring proper operation of the device, you should follow the recommendations given below.

# Rules for safe handling with high voltage

#### Attention!

All operations with this device should only be performed by personnel with sufficient qualifications.

# Caution, High Voltage!

Before installing the board in the system, make sure that the mains power supply is off. The same also applies to the installation of expansion boards.

There is a serious risk of electric shock during installation, repairs, and maintenance of the device, so always unplug the power supply cord while carrying out of works. The same also applies to the other power supply cables.

# Instructions for board handling

#### Static-sensitive device!

Electronic boards and their components are sensitive to static electricity. Therefore, special attention should be given when handling these devices to ensure their safety and operability.

- Do not leave the board in the non-operating position without protective packaging.

- ✓ If possible, always work with the board in workplaces protected against static electricity. Should this not be possible, the user should remove the static charge before touching the product with their hands or tools. The best way to do so is by touching any metal part of the system enclosure.

- ✓ It is especially important to observe precautions when replacing expansion boards, memory modules, jumpers, etc. If the product is equipped with batteries to power the memory or real-time clock, avoid placing the board on conducting surfaces such as anti-static mats or sponges. They can cause short circuits and damage the battery and the board's conducting circuits.

# General rules of usage

- In order to keep the warranty, the product must not be altered or changed in any way. Any changes and improvements unauthorized by Fastwel Group other than those contained in this User Manual or received from the technical support service of Fastwel Group in the form of a set of instructions for their implementation will void the warranty.

- This device should be installed and connected only to systems that meet all necessary technical and climatic requirements. This also applies to the operating temperature range of a particular version of the board. You should also consider the temperature limits of the batteries installed on the board.

- Follow the instructions in this User Manual only when performing all necessary installation and configuration operations.

- Retain the original packaging for storing products in the future or to transport in case of a warranty claim. If it is necessary to transport or store the board, pack it the same way as it was packed at the time of receipt.

- Proceed with extra caution when handling and unpacking the device. Follow the instructions given below.

## MANUFACTURER'S WARRANTIES

## Warranty liabilities

The manufacturer guarantees that CPC316 meets the requirements of technical specifications of the "CPU MODULE IN PC104 FORMAT" TU 4013-004-52415667-05 provided that the Consumer complies with the operating conditions, transportation, storage, installation and mounting, set by the operational documents.

The manufacturer guarantees that the products supplied by it will not show any manufacturing defects and materials used in compliance with the rules of operation and maintenance during the warranty period established at the moment. The Manufacturer's obligation under this warranty is to repair or replace, free of charge, any defective electronic component included in the returned product.

Products that failed through the Manufacturer's fault during the warranty period will be repaired free of charge. In other cases, the Consumer will be billed based on current remuneration rates and the cost of consumables.

# Right of limitation liability

The manufacturer is not responsible for any damages caused to the Consumer's property due to the failure of the product in the process of its use.

#### Warranty period

The warranty period for the manufacturer's products is 36 months from the date of sale (unless otherwise provided by the delivery agreement).

For customized products, the warranty period is 60 months from the date of sale (unless otherwise provided by the delivery agreement).

# The warranty set forth above does not extend to and shall not apply to:

- 1. Products, including software, which have been repaired or altered by other than Fastwel personnel, unless Buyer has properly altered or repaired the products in accordance with procedures previously approved in writing by Fastwel.

- 2. Products, which have been subject to power, supply reversal, misuse, neglect, accident, or improper installation.

## Returning a product for repair

- 1. Apply to Fastwel Company or to any of the Fastwel's official representatives for the Product Return Authorization.

- 2. Attach a failure inspection report with a product to be returned in the form, accepted by customer, with a description of the failure circumstances and symptoms.

- 3. Carefully package the product in the antistatic bag, in which the product had been supplied. Failure to package in antistatic material will VOID all warranties. Then package the product in a safe container for shipping.

- 4. The customer pays for shipping the product to Fastwel or to an official Fastwel representative or dealer.

# Transportation, Unpacking and Storage

# **Transportation**

The modules should be transported in the separate manufacturer's packaging (container), consisting of an individual antistatic packaging and a cardboard box, in closed transport (road, rail, air in heated and sealed compartments) under storage conditions 5 according to the GOST standard 15150-69 or under storage conditions 3 for sea transportation.

It is allowed to transport the modules packed in individual antistatic bags in manufacturer's group packaging (container).

Transportation of packaged modules should be carried out in accordance with the rules of transportation of goods currently valid for this type of transport.

During handling operations and transportation, the packed modules should not be subjected to sudden shocks, drops, impacts and precipitation. The packed modules should be placed on the vehicle in such a way as to preclude their further movements.

# Unpacking

Before unpacking, after transportation at negative ambient temperatures, the modules must be kept for 6 hours under storage conditions 1, in accordance with the GOST standard 15150-69.

Do not place the packed modules near any heat sources before unpacking.

When unpacking the modules, it is necessary to observe all precautions to ensure their safety, as well as marketable condition of manufacturer's consumer packaging.

When unpacking, it is necessary to check the modules for any external mechanical damages after transportation.

# **Storage**

Storage conditions of the modules 1 comply with the GOST standard 15150-69.

# 1 Description and operation

# 1.1 Purpose of the device

The device is a highly integrated solution based on the x86 platform for the use in real time systems of management, production control, data acquisition and processing and can operate in the standalone and slave mode. Connection of the main I/O means (VGA monitor, LVDS panel, keyboard, printers, USB) enables the device to be used in systems with operator participation. For data storage, both an integrated storage device or a Compact Flash card, and external USB devices can be used.

The product is made in PC/104-plus format and enables you to solve most of the tasks of inputoutput of digital signals. In addition, the device makes it possible to promptly replace the operating software of the built-in FPGA, which gives additional opportunities for its adaptation to specific tasks.

Expanding device's functionality is also possible by connecting additional expansion modules of the PC/104 and PC/104-plus format.

The product can be connected to RS-232, RS-485 and Ethernet networks, which makes it possible to use it in distributed input-output and information processing systems.

# 1.2 Technical specifications

## **Vortex86DX3 CPU (x86-compatible instruction set):**

- Clock rate: 800 MHz;

- Number of physical cores: 2;

- 32 x bit x86 core;

- 32 bit memory bus;

- L1 cache (64 KB);

- L2 cache (512 KB);

#### RAM:

- DDR3 SDRAM 2 GB (soldered onboard);

- Memory bus width: 32 bit;

- Memory bus operating frequency: 667 MHz;

### Video subsystem:

- video controller with 2D accelerator;

- port for connection of VGA monitor with resolution up to 1920x1080, color 32 bit;

- port for connection of LVDS panel with resolution up to 1920x1080, color 32 bit;

#### PCI104 bus (PCI 33 MHz 32 bit);

## PC104 bus (ISA 8/16 bit, 8/16 MHz);

#### Non-volatile RAM:

- volume: 32 KB;

- implemented using the FRAM technology, SPI interface;

- battery power supply is not required;

#### Flash-drive:

- connected to SATA interface;

- 8 GB NAND Flash (pSLC);

- read/write rate of 100/80 MB/s;

- integrated system of wear control and ECC;

## LAN ports:

- 1 x Fast Ethernet 10/100 Mb/s port;

- 1 x Gigabit Ethernet 10/100/1000 Mb/s port;

- system isolation of 500V;

# ■ USB ports (host):

- support of USB 1.1, USB 2.0 (HS, FS, LS);

- connection of up to 4 devices;

#### Connector for Compact Flash (Type I/II):

- support of UltraDMA-5 mode;

#### Serial ports:

- COM1: RS-232 (9-wire);

- COM2: RS-232 (9-wire);

- exchange rate over RS-232: up to 115.2 Kb/s;

- protection against ESD 15 kV (IEC1000-4-2);

- COM3: isolated RS-422/485 (individual system isolation 500V);

- COM4: isolated RS-422/485 (individual system isolation 500V);

- automatic (hardware) control of transmission direction for RS-485 ports;

- exchange rate over RS-422/485: up to 115.2 Kb/s <sup>1</sup>

#### GPIO port

- 8 x I/O lines:

- compatibility with the level +5V (TTL);

## ■ Universal digital I/O port2:

- 48 CMOS/TTL lines;

- output load up to 24 mA;

- possibility of changing functions (scheme) of port within the system;

- power supply voltage output +5 V @ 0.75 A for connected devices;

#### Watchdog timers:

- 2 watchdog timers, built into the processor, with a programmable event and an actuation interval of 30.5 µs...512 s;

#### Real Time Clock:

- consumption current when power is off: 2 μA<sup>3</sup>

#### Integrated lithium battery 3V:

- CR2032, standard capacity 200 mA\*h;

- Buzzer

- Isolated port of reset / interrupt source

<sup>&</sup>lt;sup>1</sup>Exchange rate over serial ports is defined by the frequency divider register.

<sup>&</sup>lt;sup>2</sup>The electrical parameters of the digital input/output channels are determined by the parameters of the installed buffer microcircuit SN74LVC1T45DCKTE4 (Texas Instruments, <a href="www.ti.com">www.ti.com</a>).

<sup>&</sup>lt;sup>3</sup> Standard value under normal conditions.

## Digital temperature sensor

Measuring the temperature of the CPU board from - 55 to +125 °C, typical absolute error of temperature measurement<sup>4</sup>:

- $\pm$  0.5 °C (within the range from +10 to +50 °C);

- ± 1.0 °C (within the range from 10 to +85 °C);

- ± 2.0 °C (within the range from -40 to +85 °C);

resolution and price per unit for the least significant bit: 12 bit + character / 0.0625 °C conversion time is up to 1000 ms.

- Measuring secondary supply voltages of the module by an integrated ADC

- Compatibility with operating systems:

- FreeDOS, Microsoft™ MS-DOS® 6.22

- Linux 2.6, 3.2

- Windows Embedded Standard 7

- Console serial ports: COM1 / COM2 / COM3 / COM4;

- Power supply voltage: from 4.25 to 5.25 V

- operating temperature range: from -40 to +85 °C

Storage conditions for the modules: 1 according to the GOST standard 15150-69

- Humidity: from 5 to 95%, at +25 °C, non-condensing;

- Resistance to multiple/single shocks: 50/150 g;

- Vibration resistance: 10 g for frequencies from 50 to 2000 Hz;

- MTBF 5: min. 100,000 hours;

- **Dimensions**, max: 116 x 101.56 x 24.13 mm;

- Module's weight, max.: 0.2 kg;

- Packed weight, max.: 0.4 kg;

## 1.3 Connection to the device

Below is the typical list of interface boards and devices, which may be connected to the device:

- Devices with Ethernet 10 / 100 / 1000 Mb/sec interface;

- Devices compatible with RS-232;

- RS-485 multiuser networks;

- Compact Flash memory cards;

- USB devices, type 1.1 and 2.0 (Full-speed, High-speed), including devices of the USB Mass Storage Device type;

- Keyboard, mouse (USB ports);

- Monitors and TFT panels;

<sup>&</sup>lt;sup>4</sup> The measurement accuracy of integrated sensors is not standardized and is determined by the data in the chip manufacturer's documentation.

<sup>&</sup>lt;sup>5</sup>The MTBF value is calculated using the Telcordia Issue 1 calculation model (Method I Case 3) for continuous operation when located on the ground under conditions corresponding to the climatic category Moderately Cold Climate 4 in accordance with GOST 15150-69 standard, at an ambient temperature of +30°C.

- PC-compatible printer (USB port);

- RTU modules with galvanic isolation (via the MPB-24 or TBI-24/16L and TBI-24LC boards);

- Terminal boards for the digital I/O port for passing from IDC-xx and IDC2-xx connectors to WAGO terminal strips: TIB972.

#### 1.3.1 Terminal Board TIB972

TIB972-01 – is a 26 pin terminal board: WAGO terminal strip of the 736 series, IDC2-26 connectors (pitch of 2 mm) and IDC-26 (pitch of 2.54 mm).

Pin numbers of the WAGO terminal strip, series 736, are shown on the PCB.

Fig 1-1 - Terminal board TIB972-01

Table 1-1 - Terminal board TIB972-01 (Table of pins)

| WAGO 736-413 | IDC2-26 | IDC-26 |

|--------------|---------|--------|

| 1            | 1       | 1      |

| 2            | 2       | 2      |

| 3            | 3       | 3      |

|              |         |        |

| 26           | 26      | 26     |

# 1.4 Power Supply

The device's power supply should meet the requirements specified in Table 1-2.

The device is powered through the PC/104 and PC/104-plus connectors (if installed). If you need to supply power from an external source, you can use the additional XP11 power supply connector (4-pin AMP 4-171826-4 connector).

The power supply should provide the starting current specified in Table 1-2. It is also permitted to use a power supply with a current limiting mode for at least 3.0 A (excluding any peripherals connected). When choosing a power supply, the starting current and the current consumption of expansion modules and other devices connected to the device ports, should be considered.

The device is equipped with an active protection circuit against short circuit and against supplying reverse voltage. There is also a surge protection against overvoltage above 30 V (direct or reverse polarity) by parallel connection of the TVS protection diode SM6T33CA. In case of long-term supply of more than 30 V supply voltage (direct or reverse polarity), the protective diode may fail. There are following consumers of the +5 V input power supply:

- 1) Device (+5V @ 1.5A);

- 2) External equipment connected to USB ports (4x ports, maximum consumption of each port is +5V @ 0.5A);

- 3) External equipment, connection to UNIO ports (2 x ports, maximum consumption of each port is +5V @ 0.75A);

- 4) LVDS panel (1 x port, maximum consumption of +3.3V @ 0.75A);

- 5) External equipment, connection to GPIO port (maximum consumption of +5V @ 0.75A);

- 6) External equipment, connected to RS-232 ports (2 x ports, maximum consumption of +5V @ 0.75A).

The maximum possible load-carrying capacity for the "+5 V" power supply voltage is 6 A. If the value is exceeded, the active protection of the device will be triggered and the input power will be disconnected, which will be automatically restored when the load current falls below the limit value, in which case the device will restart.

Table 1-2 - Requirements for the external power supply parameters

| Version                | Power supply voltage, V | Voltage limiting values, V | Load current, A | Start-up current, A |

|------------------------|-------------------------|----------------------------|-----------------|---------------------|

| CPC316-01<br>CPC316-02 | +5V                     | from +4.75 to +5.25        | 2.0             | 3.0                 |

| without peripherals    |                         |                            |                 |                     |

Recommended mating part for additional XP11 power connector (AMP 4-171826-4): AMP 4-171822-4 and AMP 170263-1 sets of pins (available for order as ACS00038 kit (socket and pins) or as ACS00038-01 kit (socket, pins and 1 m long wires).

Table 1-3 – Purpose of the power supply connector pins

| Power supply connector: AMP 4-171822-4 |          |  |  |

|----------------------------------------|----------|--|--|

| Pin#                                   | Function |  |  |

| 1                                      | +5 V     |  |  |

| 2                                      | GND      |  |  |

| 3 GND                                  |          |  |  |

| 4                                      | -        |  |  |

# 1.5 Block diagram

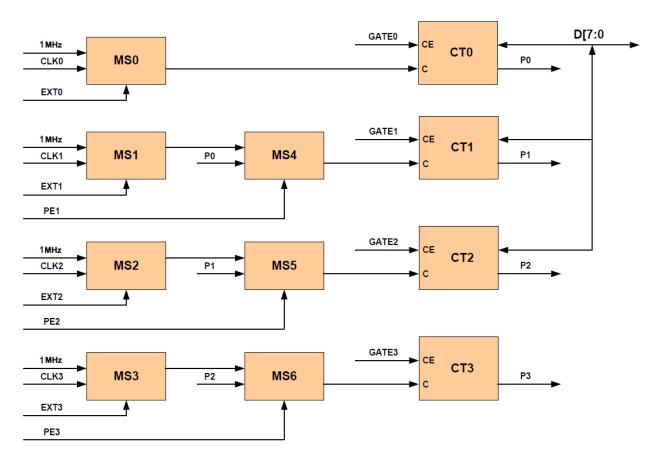

Fig. 1-2 - Block diagram of the device

# 1.6 Location of main elements

Fig. 1-3 – Location of main elements of the device on the top side of the board

Fig. 1-4 Location of the main elements of the device on the bottom side of the board

The assignment of connectors and switches is given in paragraph 1.9 Structure and functioning and paragraph 3.1 Setting the switches.

The device is made in accordance with the *PC/104-plus* v.2.0 specification.

On the top side, there is a deviation from the specification for the maximum height of components (8.76 mm) in the area of the processor's heatsink: 10.5 mm.

On the bottom side, there is a deviation from the specification for the maximum height of the components (4.83 mm). These components include:

- XP7 connector for Compact Flash (8.3 mm);

- socket X7 for CR2032 battery (4.95 mm).

# 1.7 Versions

| Item No. | Version                         | Description                                                                                                                                                                           |

|----------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | CPC316-01<br>IMES.467444.114    | Vortex86DX3 CPU (800 MHz Dual Core); 2 GB RAM; 8 GB flash drive, Compact Flash; VGA; LVDS; Audio port; 2 x LAN, 2 x RS-232, 2 x RS-422/485, 4 x USB2.0; 48 x DIO; PC/104-plus format. |

| 2        | CPC316-02<br>IMES.467444.114-01 | Vortex86DX3 CPU (800 MHz Dual Core); 2 GB RAM; 8 GB flash drive, Compact Flash; VGA; 2 x LAN, 2 x RS-232, 2 x RS-422/485, 4 x USB2.0; 48 x DIO; PC/104 format.                        |

#### Note

The modules with conformal coating obtain the "\COATED" inscription when ordered.

# 1.8 Delivery checklist

The standard delivery checklist includes:

- 1. CPC316 CPU Module

- 2. Installation kit 1 pcs.

- 3. Packaging.

The installation kit for IMES.467941.053 includes:

- 1. Jumper 1 pcs.

- 2. Rack WE 4 pcs.

- 3. DIN7985-M3x6-A2 screw 4 pcs.

- 4. DIN985-M3-A2 nut 4 pcs.

- 5. DIN125-3,2-A2 washer 4 pcs.

- 6. DIN6798A-3,2-A2 washer 4 pcs.

# 1.9 Structure and functioning

#### 1.9.1 Processor

The device is based on a dual-core x86-compatible 32-bit Vortex86DX3 processor with low power consumption, made using 45nm technology. The operating frequency of the processor is 800 MHz. The detailed information on the processor, as well as the current versions of drivers and system software are posted on the manufacturer's website at: <a href="http://www.vortex86.com">http://www.vortex86.com</a>.

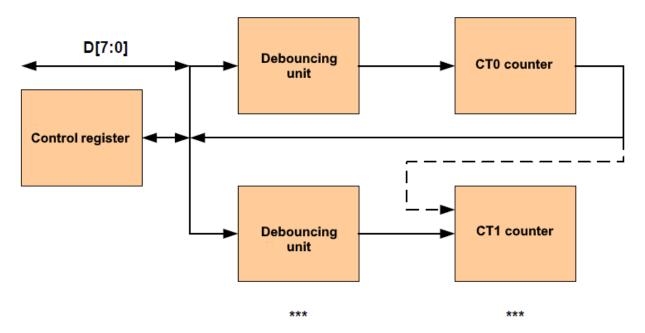

## 1.9.2 Supervisor, Watchdog, Reset

The device includes a power supply supervisor (a microchip that monitors the power supply voltage of the device), as well as 3 watchdog timers: 2 watchdog timers integrated into the CPU (WDT0, WDT1). The supervisor generates a hardware reset signal when the

"3.3V" power supply voltage drops below 3.08V, as well as an interrupt signal when the "5V" main power supply voltage drops below 4.6V, which makes it possible, if necessary, to save user data in non-volatile RAM (setting interrupts via internal FPGA registers).

The watchdog timer can be used to avoid software freeze-ups. The WDT0 and WDT1 watchdog timers are triggered in the absence of software confirmations for 30.5 µs ... 512 sec. The internal watchdog timer is started in the SYSTEM BIOS SETUP. It is possible to configure the operation of the internal watchdog timer with or without generation of a hardware reset signal.

The device is reset when the power is turned on, by software, as well as by pressing the "RESET" button located on the side panel of the controller.

#### 1.9.3 RAM

The device uses dynamic DDR3 SDRAM with a total size of 2 GB and operating at a frequency of 667 MHz as a system memory. The memory module cannot be expanded.

#### 1.9.4 NV SRAM

The device has 256 byte integrated non-volatile RAM for storing configuration data (CMOS) written by the SETUP program built into the BIOS.

In addition, it is possible to use the integrated non-volatile memory of 32 KB, made by FRAM technology and does not require battery power. The SPI interface of the processor is used to access the static non-volatile memory.

## 1.9.5 Read Only Memory (FLASH BIOS)

For storing the basic input / output system (hereinafter referred to as BIOS), the device uses flash-memory chip of 2 MB, integrated into the Vortex86DX3 processor chip.

## 1.9.6 Flash drive (SATA NAND Flash)

The device contains a flash memory chip using NAND technology (pSLC). It can be used as a boot drive. To arrange access to the NAND Flash, a controller with an integrated error correction and wear leveling system is used, connected to the SATA interface of the processor.

The integrated drive has a volume of 8GB (real available volume is 7.8GB).

Compact Flash cards and external USB drives can be used as additional drive memory.

## 1.9.7 Slot for Compact Flash cards

The Compact Flash (CF type I / II) can be connected to the device via XP7 (N7E50-M516RB-50, 3M) and set as Master on the Primary IDE channel.

The Compact Flash can be used as the boot drive. Supported mode up to UltraDMA-5.

#### Caution!

WHEN USING THE DEVICE UNDER SEVERE OPERATING CONDITIONS, IT IS NECESSARY TO TAKE ADDITIONAL MEASURES TO FIX THE COMPACT FLASH IN THE CONNECTOR! External view and overall dimensions of the additional fastener 7E50-C016-00, 3M (not included in the product delivery checklist) are shown in Figure 1-6.

Fig. 1-5 - Fastener for Compact Flash

#### 1.9.8 COM1-4 serial ports

The device controller has 4 x asynchronous serial ports:

- COM1, COM2 RS-232 (5-wire interface, non-insulated);

- COM3, COM4 RS-422/485 (3- or 5-wire connection, insulated 500 V).

RS-232 COM1 (0x3F8h) and COM2 (0x2F8h) serial ports, as well as RS-422/485 COM3 (0x3E8h) and COM4 (0x2E8h) ports are implemented on the UART controllers integrated into the Vortex86DX3.

The COM1 (RS-232) port of the CP316 module corresponds to the "serial port 5" of the Vortex86DX3 CPU, COM2 (RS-232) – "serial port 6", COM3 (RS-422/485) – "serial port 1", COM4 (RS-422/485) – "serial port 2".

COM3 (XP8) and COM4 (XP4) ports operate in the RS-422/485 mode and provide galvanic isolation up to 500 V (each port has individual isolation from the system). The maximum data transfer rate is 230.4 Kb/sec. The ports are routed to 5-pin B 5B-PH-KL (JST) connectors. For manufacturing the cable, it is recommended to use a PHR-5 socket, JST with SPH-002T-P0.5S pins, JST (available for order as a set ACS00031-01) and a shielded twisted pair.

Table 1-4 - Purpose oft he pins of RS-422/485 (XP8, XP4) ports

| COM3-4: B 5B-PH-KL (JST) |                   |                   |  |  |

|--------------------------|-------------------|-------------------|--|--|

| Pin#                     | Function (RS-422) | Function (RS-485) |  |  |

| 1                        | TX+               | RTxD+             |  |  |

| 2                        | TX-               | RTxD-             |  |  |

| 3                        | RX+               | -                 |  |  |

| 4                        | RX-               | -                 |  |  |

| 5                        | GNDS              | GNDS              |  |  |

The "GNDS" circuit corresponds to the signal isolated "ground" of the interface, the GNDS circuits of the different ports are isolated from each other and are not interconnected. By setting the X6 (COM3) and X7 (COM4) jumpers, the matching circuits are connected to the signal lines of the RS-422 or RS-485 interfaces and the operating mode is set.

#### Attention!

For proper operation of RS-422/485 transmit/receive unit in a multiuser network, use the appropriate jumpers to install 120 Ohm terminators at the 2 most distant network nodes, as well as the 680 Ohm biasing resistors (at one or two of the most distant network nodes).

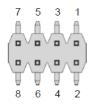

Table 1-5 - Configuration of the COM3 (X6) port

| Jumper               | Description                               |  |

|----------------------|-------------------------------------------|--|

| X6[1-2] <sup>6</sup> | Biasing resistor is set on the line TX+   |  |

| X6[3-4]              | Biasing resistor is set on the line TX-   |  |

| X6[5-6]              | Half-duplex mode is selected <sup>7</sup> |  |

| X6[7-8]              | Half-duplex mode is selected              |  |

Table 1-6 - Configuration of the COM4 (X7) port

| Jumper               | Description                               |  |

|----------------------|-------------------------------------------|--|

| X7[1-2] <sup>8</sup> | Biasing resistor is set on the line TX+   |  |

| X7[3-4]              | Biasing resistor is set on the line TX-   |  |

| X7[5-6]              | Half-duplex mode is selected <sup>9</sup> |  |

| X7[7-8]              | Half-duplex mode is selected              |  |

<sup>&</sup>lt;sup>6</sup> The default switch positions are highlighted in bold.

<sup>&</sup>lt;sup>7</sup> The mode is selected only when the both jumpers are installed.

<sup>&</sup>lt;sup>8</sup> The default switch positions are highlighted in bold.

<sup>&</sup>lt;sup>9</sup> The mode is selected only when the both jumpers are installed.

Each port contains lightning protection circuits based on resettable fuses and gas discharge elements. The port also contains TVS diode-based pulse interference protection circuits. The diagram of the output stages of the COM3 port is shown below (the COM4 port has a similar circuit design).

The maximum number of modules connected to the RS-485 network together with the device amounts to 128, provided that the input impedance of the RS-485 drivers is at least 96 kOhm.

Fig. 1-6 - Output stages of RS-422/485 ports of the device

Fig. 1-7 - Connecting modules via RS-485 interface

Fig. 1-8 - Connecting modules via RS-422 interface

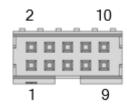

The COM1 (XP13) and COM2 (XP14) ports operate in RS-232 mode. The maximum baud rate for COM1 and COM2 is 115.2 Kb/s. The ports are fully software compatible with the 16550 UART model.

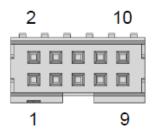

Each port is routed to a vertical two-row 10-pin connector of the IDC2-10 type with a pitch of 2 mm (98414-G06-10LF, FCI). As a mating part, it is necessary to use a 10-pin socket 89947-710LF (FCI) for a ribbon cable with a pitch of 1 mm. A ready-made cable (IDC2-10 - DB9M) ACS00023-04 is available for ordering, cable length: 17 cm.

The both ports can be used for console I/O and file downloads. A null-modem cable is required to communicate with a PC used as a hyperterminal.

By default, the console port is COM1 (port settings in the terminal program PuTTY, Hyperterminal: rate - 115200 bit/s, data bit - 8, stop bit - 1, no parity check).

Table 1-7 - Purpose of the pins of RS-232 (XP13, XP14) ports

| COM1, COM2: 98414-G06-10LF (FCI) |          |      |          |  |

|----------------------------------|----------|------|----------|--|

| Pin#                             | Function | Pin# | Function |  |

| 1                                | DCD      | 2    | DSR      |  |

| 3                                | RXD#     | 4    | RTS      |  |

| 5                                | TXD#     | 6    | CTS      |  |

| 7                                | DTR      | 8    | RI       |  |

| 9                                | GND      | 10   | +5V_EXTR |  |

The base addresses and interrupts for serial ports are set in BIOS Setup. By default, the following base addresses/interrupts are set for serial ports in BIOS Setup:

```

COM1 (RS-232): 0x3F8 / IRQ4, [115200 8,n,1] <sup>10</sup> COM2 (RS-232): 0x2F8 / IRQ3, [115200 8,n,1] COM3 (RS-485): 0x3E8 / IRQ4, [115200 8,n,1] COM4 (RS-485): 0x2E8 / IRQ3, [115200 8,n,1]

```

The baud rate for serial ports can be set in the BIOS Setup. The exchange rate is determined by the value of the CPU frequency divider register. The value of the divider and the data exchange rate is calculated using the following formulas:

$$DIV = F / (16 \cdot BR), BR=F / (DIV \cdot (SM + FD))$$

- F internal generator frequency, MHz (F = 1.8432 / 24 / 48);

- DIV (divider) divider value (for F = 1.8432, 24 and 48 MHz minimum value DIV = 1);

- BR (baud rate) required exchange rate, bit/sec;

- SM (sampling mode) Base divider value (SM = 16).

#### Attention!

The receiver allows the exchange rate value downward bias by 3.0% and upward bias by 2.5%.

Table 1-8 - Frequency divider values for serial ports

| Exchange    | F=1.84  | F=1.8432 MHz |         | F=24 MHz |         | F=48 MHz |  |

|-------------|---------|--------------|---------|----------|---------|----------|--|

| rate, bit/s | Divider | Error, %     | Divider | Error, % | Divider | Error, % |  |

| 300         | 384     | _            | 5000    | -        | 10000   | -        |  |

| 600         | 192     | _            | 2500    | -        | 5000    | _        |  |

| 1200        | 96      | -            | 1250    | -        | 2500    | -        |  |

| 2400        | 48      | -            | 625     | -        | 1250    | -        |  |

| 3600        | 32      | -            | 417     | -        | 625     | -        |  |

| 4800        | 24      | -            | 312     | -        | 625     | -        |  |

| 7200        | 16      | -            | 208     | -        | 417     | -        |  |

| 9600        | 12      | -            | 156     | -        | 312     | -        |  |

| 19200       | 6       | -            | 78      | -        | 156     | -        |  |

| 38400       | 3       | -            | 39      | -        | 78      | _        |  |

| 57600       | 2       | -            | 26      | -        | 52      | -        |  |

| 115200      | 1       | -            | 13      | -        | 26      | -        |  |

| 200000      | -       | -            | _       | -        | _       | -        |  |

| 230400      | -       | -            | _       | -        | 13      | _        |  |

| 250000      | -       | -            | 6       | -        | 12      | _        |  |

| 300000      | -       | -            | 5       | -        | 10      | _        |  |

| 460800      | -       | -            | -       | -        | -       | _        |  |

<sup>&</sup>lt;sup>10</sup> Baud rate 115.2 Kbaud, 8 bits, no parity check, 1 stop bit

## 1.9.9 USB1-4 ports

The Device Controller has 4 x USB Host ports supporting USB 1.1 and USB 2.0 specifications. The operating mode of the interfaces is set in the BIOS Setup menu.

Each of the channels has an independent power supply control circuit and power protection (+5 V, 500 mA).

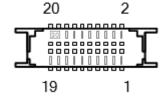

All 4 x channels are routed to one XP19 connector: IDC2-20, 20-pin, two-row male connector with a pitch of 2 mm, 98414-G06-20LF (FCI).

A 20-pin socket 89947-720LF (FCI) to a flat ribbon cable with a pitch of 1 mm or a 20-pin socket 10073599-020LF (FCI) with pins 77138-101LF (FCI) should be used as a mating part.

Table 1-9 - Purpose of pins of the USB (XP19) ports

|       | USB1-4: 98414-G06-20LF (FCI) |      |             |  |

|-------|------------------------------|------|-------------|--|

| Pin # | Function                     | Pin# | Function    |  |

| 1     | +5 V @ 0.5A                  | 2    | +5 V @ 0.5A |  |

| 3     | D-                           | 4    | D-          |  |

| 5     | D+                           | 6    | D+          |  |

| 7     | GND                          | 8    | GND         |  |

| 9     | -                            | 10   | -           |  |

| 11    | +5 V @ 0.5A                  | 12   | +5 V @ 0.5A |  |

| 13    | D-                           | 14   | D-          |  |

| 15    | D+                           | 16   | D+          |  |

| 17    | GND                          | 18   | GND         |  |

| 19    | -                            | 20   | -           |  |

# 1.9.10 LAN1 and LAN2 ports

The device contains 2 x LAN ports.

LAN1 port supports 10/100/1000 Mbit operation modes and is based on Intel WGI210IT controller. The LAN2 port supports 10/100 Mbit operation modes and is implemented on the basis of a controller built into the Vortex86DX3 microprocessor.

The ports provide galvanic isolation up to 500 V (each port is individually isolated from the system). Each port is routed to a two-row 10-pin connector with a pitch of 2 mm, 98414-G06-10LF (FCI). 10-pin socket 89947-710LF (FCI) for a flat ribbon cable with a pitch of 1 mm or a 10-pin socket 10073599-010LF (FCI) with pins 77138-101LF (FCI).

Table 1-10 - Purpose of pins of the LAN1 (XP10) port

| LAN1: 98414-G06-10LF (FCI) |            |      |            |

|----------------------------|------------|------|------------|

| Pin #                      | Function   | Pin# | Function   |

| 1                          | MD0+ / TX+ | 2    | MD0- / TX- |

| 3                          | MD1+ / RX+ | 4    | MD1- / RX- |

| 5                          | MD2+       | 6    | MD2-       |

| 7                          | MD3+       | 8    | MD3-       |

| 9                          | -          | 10   | -          |

Table 1-11 - Purpose of pins of the LAN2 (XP15) port

| LAN2: 98414-G06-10LF (FCI) |          |      |          |

|----------------------------|----------|------|----------|

| Pin#                       | Function | Pin# | Function |

| 1                          | TX+      | 2    | TX-      |

| 3                          | RX+      | 4    | RX-      |

| 5                          | -        | 6    | -        |

| 7                          | -        | 8    | -        |

| 9                          | -        | 10   | -        |

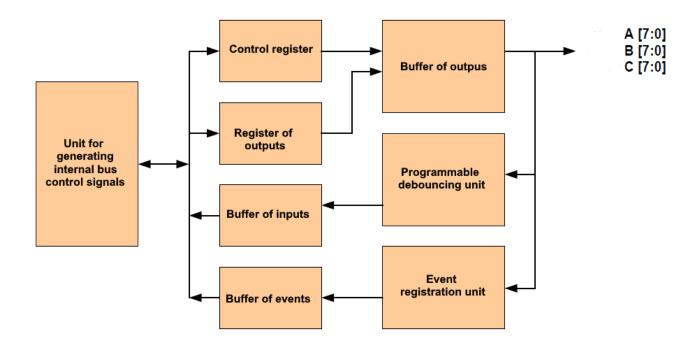

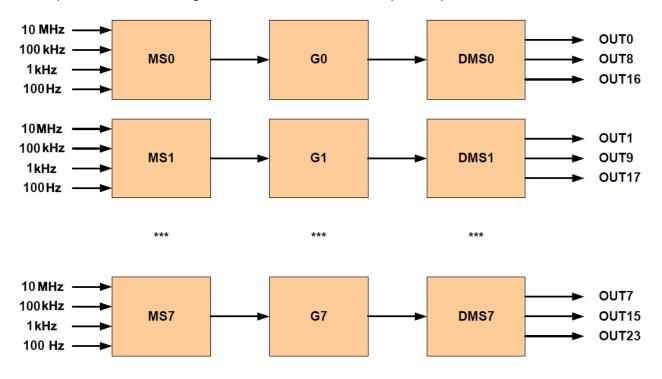

## 1.9.11 Ports of the digital I/O ports UNIO (DIO)

The device includes 2 x universal ports of digital input-output IO\_A [23: 0] (XP16) and IO\_B [23: 0] (XP18), which are compatible by output pins and control with the UNIO96-5 module. The ports are implemented on the XC6SLX16-2CSG324I field programmable gate array (FPGA) and are designed for input/output of 48 logic signals.

Overvoltage protection for 5.6 V is installed on each line (based on TVS diodes RClamp0524, designed to protect against pulse interference). The transmission direction is controlled by groups of channels or per channel, depending on the loaded configuration. The buffer elements based on the SN74LVC1T45DCKTE4 microchips with control of the transmission direction are used to provide power supply voltage output up to +5 V; to read the status of channels during output operation, groups of buffer elements based on SN74LVC2G125YZPR are used with the arrangement of switching channel groups (each group consists of 8 channels).

Fig. 1-9 - Diagram of one channel of the port of digital input-output

The function (scheme) of the port can be changed directly in the system (ISP technology, insystem-programming) without turning off the power.

The port channels can be used to control RTU modules with galvanic isolation, pulse counting, frequency measurement and generation, time diagrams, etc.

# Attention!

When connecting external devices to the digital I/O port, using the common wire (pin # 26 of the IDC2-26 connector) is mandatory.

#### Attention!

It is recommended to use an additional connection to the high (+5 V) or low (GND) level of the digital I/O port's lines directly in the devices connected to these ports (recommended resistance rated value is 10 kOhm). In this case, the selected levels (+5 V or GND) on the CPU module and the connected external board should match.

When delivered, the device has the installed firmware n00. The change of the port configuration version is made by software and is carried out by recording to the corresponding control register, see the **Register for selecting the active firmware of the digital I/O port**.

#### Attention!

Firmware of the FPGA chip, which is used as the basis for the digital I/O port, is incompatible with the firmware of other modules. Using the firmware of another module may cause device malfunctions.

Connecting 10 kOhm resistors for binding the port lines to the "+5V" power supply voltage or to the "GND" ground is carried out with the X20 switch.

Table 1-12 - Binding levels of UNIO ports lines (X20)

| Jumper      | Description                                                                        |

|-------------|------------------------------------------------------------------------------------|

| X20[1-3] 11 | Binding the lines IO_A[23:0] via resistors 10 kOhm to the power supply voltage +5V |

| X20[3-5]    | Binding the lines IO_A[23:0] via resistors 10 kOm to the ground (GND)              |

| X20[2-4]    | Binding the lines IO_B[23:0] via resistors 10 kOhm to the power supply voltage +5V |

| X21[4-6]    | Binding the lines IO_B[23:0] via resistors 10 kOhm to the ground (GND)             |

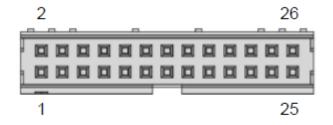

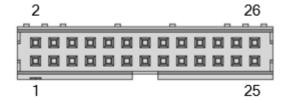

Each port is routed to a two-row 26-pin connector with a pitch of 2 mm, 98424-G52-26LF (FCI). A 26-pin socket 89947-726LF (FCI) for a flat ribbon cable with a pitch of 1 mm or a 20-pin socket 10073599-026LF (FCI) with the pins 77138-101LF (FCI) should be used as a mating part.

Table 1-13 - Purpose of the pins of DIO (UNIO IO\_A[23:0], XP16) connector

| UNIO IO_A: 98424-G52-26LF (FCI) |          |  |      |          |

|---------------------------------|----------|--|------|----------|

| Pin#                            | Function |  | Pin# | Function |

| 1                               | IO_A(12) |  | 2    | +5V_EXTA |

| 3                               | IO_A(13) |  | 4    | IO_A(10) |

| 5                               | IO_A(14) |  | 6    | IO_A(11) |

| 7                               | IO_A(15) |  | 8    | IO_A(9)  |

| 9                               | IO_A(23) |  | 10   | IO_A(8)  |

| 11                              | IO_A(21) |  | 12   | IO_A(22) |

| 13                              | IO_A(16) |  | 14   | IO_A(20) |

| 15                              | IO_A(18) |  | 16   | IO_A(17) |

| 17                              | IO_A(19) |  | 18   | IO_A(7)  |

| 19                              | IO_A(0)  |  | 20   | IO_A(6)  |

| 21                              | IO_A(1)  |  | 22   | IO_A(5)  |

| 23                              | IO_A(2)  |  | 24   | IO_A(4)  |

| 25                              | IO_A(3)  |  | 26   | GND      |

<sup>&</sup>lt;sup>11</sup> The default switch positions are highlighted in bold

| Table 1-14 – Purpose of pins of the DIO (UNIO IO_B[23:0], XP18) connector |

|---------------------------------------------------------------------------|

|---------------------------------------------------------------------------|

| UNIO IO_B: 98424-G52-26LF (FCI) |          |  |       |          |

|---------------------------------|----------|--|-------|----------|

| Pin#                            | Function |  | Pin # | Function |

| 1                               | IO_B(12) |  | 2     | +5V_EXTB |

| 3                               | IO_B(13) |  | 4     | IO_B(10) |

| 5                               | IO_B(14) |  | 6     | IO_B(11) |

| 7                               | IO_B(15) |  | 8     | IO_B(9)  |

| 9                               | IO_B(23) |  | 10    | IO_B(8)  |

| 11                              | IO_B(21) |  | 12    | IO_B(22) |

| 13                              | IO_B(16) |  | 14    | IO_B(20) |

| 15                              | IO_B(18) |  | 16    | IO_B(17) |

| 17                              | IO_B(19) |  | 18    | IO_B(7)  |

| 19                              | IO_B(0)  |  | 20    | IO_B(6)  |

| 21                              | IO_B(1)  |  | 22    | IO_B(5)  |

| 23                              | IO_B(2)  |  | 24    | IO_B(4)  |

| 25                              | IO_B(3)  |  | 26    | GND      |

## 1.9.12 RTC, SPI FRAM, lithium battery

The device is equipped with an AT-compatible real-time clock with an installed CR2032 lithium battery with a capacity of 200 mAh. The expected / typical battery service life is 7 years<sup>12</sup>. However, the battery service life is highly dependent on operating temperature and how long the system is off.

#### Important note!

If the device is turned off for a long time, it is recommended to synchronize the real-time clock with the exact time readings.

## 1.9.13 VGA and LVDS ports

The video subsystem of the device is based on a video processor integrated into the Vortex86DX3 microprocessor. The video controller with a 2D accelerator function has the following technical specifications and capabilities:

- video memory size to be allocated from the system memory;

- possibility to connect RGB (VGA) monitors with max. resolution of 1920 x 1080 (60 Hz, 32 bit);

- possibility to connect LVDS panels with max. resolution of 1920 x 1080 (60 Hz, 32 bit)<sup>13</sup>.

<sup>&</sup>lt;sup>12</sup> Under normal operating conditions.

<sup>&</sup>lt;sup>13</sup> In the event of connecting both VGA monitor and LVDS panel, their maximum resolution is 1280 x 1024.

The VGA (XP2) port is routed to a two-row 10-pin connector with a pitch of 2 mm, 98414-G06-10LF (FCI). As a mating part, you should use a 10-pin 89947-710LF (FCI) socket for a ribbon cable with a pitch of 1 mm or a 10-pin 10073599-010LF (FCI) socket with 77138-101LF (FCI) pins. A ready-made cable (IDC2-10 - DB15F) ACS00027-02 is available for order, with a length of 17 cm.

Table 1-15 - Purpose of the VGA port pins (XP2)

| VGA: 98414-G06-10LF (FCI) |          |       |          |  |

|---------------------------|----------|-------|----------|--|

| Pin #                     | Function | Pin # | Function |  |

| 1                         | RED      | 2     | GND      |  |

| 3                         | GREEN    | 4     | GND      |  |

| 5                         | BLUE     | 6     | GND      |  |

| 7                         | HSYNC    | 8     | VSYNC    |  |

| 9                         | DDC_SCL  | 10    | DDC_SDA  |  |

The LVDS (XP3) port is routed to the two-row 20-pin connector with a pitch of 1.25 mm, DF13EA-20DP-1.25V (Hirose). As a mating part, you should use the 20-pin DF13-20DS-1.25C (Hirose) socket with DF13-2630SCF (Hirose) pins.

Table 1-16 - Purpose of LVDS (XP3) port pins

| LVDS: DF13EA-20DP-1.25V (Hirose) |              |       |              |

|----------------------------------|--------------|-------|--------------|

| Pin #                            | Function     | Pin # | Function     |

| 1                                | VCC (+3.3 V) | 2     | VCC (+3.3 V) |

| 3                                | DATA0+       | 4     | DATA0-       |

| 5                                | GND          | 6     | GND          |

| 7                                | DATA1+       | 8     | DATA1-       |

| 9                                | GND          | 10    | GND          |

| 11                               | DATA2+       | 12    | DATA2-       |

| 13                               | GND          | 14    | GND          |

| 15                               | DATA3+       | 16    | DATA3-       |

| 17                               | GND          | 18    | GND          |

| 19                               | CLK+         | 20    | CLK-         |

#### 1.9.14 Audio ports

The device's audio ports are based on the HDA audio controller integrated into the Vortex86DX3 microprocessor and the CS4207 24-bit audio codec (Cirrus Logic).

The codec is compatible with the SBPRO™ model.

The set of Audio ports includes: an audio output (STEREO) and a MIC (STEREO).

The DAC1 (Headphone) output of the CS4207 audio codec is used as the audio output. HDPH audio output (XP17) and MIC input (XP6) are routed to 3-pin B 3B-PH-K-S (JST) connectors.

To manufacture the cable, it is recommended to use a PHR-3, JST socket with SPH-002T-P0.5S pins, JST (available for ordering as a set ACS00031-04).

Table 1-17 - Purpose of Audio ports pins (XP17, XP6)

| Table 1 17 Talpede of Addie p |            |  |

|-------------------------------|------------|--|

| Audio out: B 3B-PH-K-S (JST)  |            |  |

| Pin #                         | Function   |  |

| 1                             | HDPH Left  |  |

| 2                             | GND        |  |

| 3                             | HDPH Right |  |

| Audio MIC: B 3B-PH-K-S (JST) |           |  |

|------------------------------|-----------|--|

| Pin #                        | Function  |  |

| 1                            | MIC Left  |  |

| 2                            | GND       |  |

| 3                            | MIC Right |  |

# 1.9.15 PC/104 expansion bus (ISA 8/16-bit)

The PC/104 (XS1) connector is designed for installing expansion modules of the PC/104 or PC/104-plus format to the module. It is allowed to install no more than 4x PC/104 expansion modules.

ISA bus operating modes: 8/16 bit, 8.3/16.6 MHz. Master mode is not supported.

The device is equipped with an AMP 1375795-5 connector (pins B10 and C19 are missing) and an AMP 1445251-1 organizer.

Table 1-18 – Purpose of XS1 connector pins: PC/104 (ISA 8/16-bit) rows A, B

| ISA: Connector of PC/104 expansion bus (2x32 + 2x20 pins), rows A, B |         |               |       |         |               |  |

|----------------------------------------------------------------------|---------|---------------|-------|---------|---------------|--|

| Pin #                                                                | Purpose | Configuration | Pin # | Purpose | Configuration |  |

| A1                                                                   | IOCHK#  | Input         | B1    | GND     | Power supply  |  |

| A2                                                                   | SD7     | Input/Output  | B2    | RESET   | Output        |  |

| A3                                                                   | SD6     | Input/Output  | В3    | +5V     | Input         |  |

| A4                                                                   | SD5     | Input/Output  | B4    | IRQ9    | Input         |  |

| A5                                                                   | SD4     | Input/Output  | B5    | -       |               |  |

| A6                                                                   | SD3     | Input/Output  | В6    | DRQ2    | Input         |  |

| A7                                                                   | SD2     | Input/Output  | В7    | -12V    | Power supply  |  |

| A8                                                                   | SD1     | Input/Output  | В8    | 0WS#    | Input         |  |

| Α9                                                                   | SD0     | Input/Output  | В9    | +12V    | Power supply  |  |

| A10                                                                  | IOCHRDY | Input         | B10   | GND     | Power supply  |  |

| A11                                                                  | AEN     | Output        | B11   | SMEMW#  | Output        |  |

| A12                                                                  | SA19    | Output        | B12   | SMEMR#  | Output        |  |

| A13                                                                  | SA18    | Output        | B13   | IOW#    | Output        |  |

| A14                                                                  | SA17    | Output        | B14   | IOR#    | Output        |  |

| A15                                                                  | SA16    | Output        | B15   | DACK3#  | Output        |  |

| A16                                                                  | SA15    | Output        | B16   | DRQ3    | Input         |  |

| A17                                                                  | SA14    | Output        | B17   | DACK1#  | Output        |  |

| A18                                                                  | SA13    | Output        | B18   | DRQ1    | Input         |  |

| A19         | SA12                                                                 | Output        |  | B19   | DACK0#  | Output        |  |

|-------------|----------------------------------------------------------------------|---------------|--|-------|---------|---------------|--|

| A20         | SA11                                                                 | Output        |  | B20   | BCLK    | Output        |  |

| A21         | SA10                                                                 | Output        |  | B21   | IRQ7    | Input         |  |

| A22         | SA9                                                                  | Output        |  | B22   | IRQ6    | Input         |  |

| A23         | SA8                                                                  | Output        |  | B23   | IRQ5    | Input         |  |

| ISA: Connec | ISA: Connector of PC/104 bus expansion (2x32 + 2x20 pins), rows A, B |               |  |       |         |               |  |

| Pin #       | Purpose                                                              | Configuration |  | Pin # | Purpose | Configuration |  |

| A24         | SA7                                                                  | Output        |  | B24   | IRQ4    | Input         |  |

| A25         | SA6                                                                  | Output        |  | B25   | IRQ3    | Input         |  |

| A26         | SA5                                                                  | Output        |  | B26   | DACK2#  | Output        |  |

| A27         | SA4                                                                  | Output        |  | B27   | TC      | Output        |  |

| A28         | SA3                                                                  | Output        |  | B28   | BALE#   | Output        |  |

| A29         | SA2                                                                  | Output        |  | B29   | +5V     | Power supply  |  |

| A30         | SA1                                                                  | Output        |  | B30   | OSC     | Output        |  |

| A31         | SA0                                                                  | Output        |  | B31   | GND     | Power supply  |  |

| A32         | GND                                                                  | Power supply  |  | B32   | GND     | Power supply  |  |

Table 1-19 - Purpose of XS1 connector pins: PC/104 (ISA 8/16-bit) rows C, D

|       |         | 4 bus expansion (2x | •     |          |               |

|-------|---------|---------------------|-------|----------|---------------|

| Pin # | Purpose | Configuration       | Pin # | Purpose  | Configuration |

| C0    | GND     | Power supply        | D0    | GND      | Power supply  |

| C1    | SBHE#   | Output              | D1    | MEMCS16# | Input         |

| C2    | LA23    | Output              | D2    | IOCS16#  | Input         |

| C3    | LA22    | Output              | D3    | IRQ10    | Input         |

| C4    | LA21    | Output              | D4    | IRQ11    | Input         |

| C5    | LA20    | Output              | D5    | IRQ12    | Input         |

| C6    | LA19    | Output              | D6    | IRQ15    | Input         |

| C7    | LA18    | Output              | D7    | IRQ14    | Input         |

| C8    | LA17    | Output              | D8    | DACK0#   | Output        |

| С9    | MEMR#   | Output              | D9    | DRQ0     | Input         |

| C10   | MEMW#   | Output              | D10   | DACK5#   | Output        |

| C11   | SD8     | Input/Output        | D11   | DRQ5     | Input         |

| C12   | SD9     | Input/Output        | D12   | DACK6#   | Output        |

| C13   | SD10    | Input/Output        | D13   | DRQ6     | Input         |

| C14   | SD11    | Input/Output        | D14   | DACK7#   | Output        |

| C15   | SD12    | Input/Output        | D15   | DRQ7     | Input         |

| C16   | SD13    | Input/Output        | D16   | +5V      | Power supply  |

| C17   | SD14    | Input/Output        | D17   | -        |               |

| C18   | SD15    | Input/Output        | D18   | GND      | Power supply  |

| C19   | -       |                     | D19   | GND      | Power supply  |

Fig. 1-10 – Numbering pins of the XS1 connector a) top view of the device, b) bottom view of the device with the organizer installed into connector

## 1.9.16 PC/104-plus expansion bus (PCI 32-bit)

The device can be connected to 3 x expansion boards of the PC/104-plus or PCI/104 format. The PCI104 bus (PCI, 32 bit, 33 MHz) supports up to 3 x PCI master devices.

The interface is routed to the XS2 connector (PCI/104 connector, 120 pins, 2 mm pitch).

The product has an AMP 1375799-1 connector and an AMP 1375801-1 organizer.

Table 1-20 - Purpose of XS2 connector pins: PCI/104 (PCU 32-bit) rows A, B